Verilog Assignments

Variable declaration assignment, net declaration assignment, assign deassign, force release.

- Procedural continuous

Legal LHS values

An assignment has two parts - right-hand side (RHS) and left-hand side (LHS) with an equal symbol (=) or a less than-equal symbol (<=) in between.

The RHS can contain any expression that evaluates to a final value while the LHS indicates a net or a variable to which the value in RHS is being assigned.

Procedural Assignment

Procedural assignments occur within procedures such as always , initial , task and functions and are used to place values onto variables. The variable will hold the value until the next assignment to the same variable.

The value will be placed onto the variable when the simulation executes this statement at some point during simulation time. This can be controlled and modified the way we want by the use of control flow statements such as if-else-if , case statement and looping mechanisms.

An initial value can be placed onto a variable at the time of its declaration as shown next. The assignment does not have a duration and holds the value until the next assignment to the same variable happens. Note that variable declaration assignments to an array are not allowed.

If the variable is initialized during declaration and at time 0 in an initial block as shown below, the order of evaluation is not guaranteed, and hence can have either 8'h05 or 8'hee.

Procedural blocks and assignments will be covered in more detail in a later section.

Continuous Assignment

This is used to assign values onto scalar and vector nets and happens whenever there is a change in the RHS. It provides a way to model combinational logic without specifying an interconnection of gates and makes it easier to drive the net with logical expressions.

Whenever b or c changes its value, then the whole expression in RHS will be evaluated and a will be updated with the new value.

This allows us to place a continuous assignment on the same statement that declares the net. Note that because a net can be declared only once, only one declaration assignment is possible for a net.

Procedural Continuous Assignment

- assign ... deassign

- force ... release

This will override all procedural assignments to a variable and is deactivated by using the same signal with deassign . The value of the variable will remain same until the variable gets a new value through a procedural or procedural continuous assignment. The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables.

These are similar to the assign - deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of a net, part-select of a net, variable or a net but cannot be the reference to an array and bit/part select of a variable. The force statment will override all other assignments made to the variable until it is released using the release keyword.

- Physical Design

- Assertion Based Verification

- Equivalence Checking

- Simulation Based

Slick on Silicon

Verilog: Continuous & Procedural Assignments

Continuous Assignment

Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types.

Regular & Implicit Assignment

Regular continuous assignment means, the declaration of a net and its continuous assignments are done in two different statements. But in implicit assignment, continuous assignment can be done on a net when it is declared itself. In the below example, `valid` is declared as wire during the assignment. If signal name is used to the left of the continuous assignment, an implicit net declaration will be inferred. In the below code `dout` is not declared as net, but it is inferred during assignment.

Procedural Assignment

We have already seen that continuous assignment updates net, but procedural assignment update values of reg, real, integer or time variable. The constant part select, indexed part select and bit select are possible for vector reg.

3 comments on “ Verilog: Continuous & Procedural Assignments ”

Excellent blog

Clearly explained.. Thanks

sir what’s your company/industry name.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

A procedural assignment updates the value of register data types.

Description:

Procedural assignments are used for updating register data types and memory data types.

The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered. In a begin-end sequential statement group, execution of the next statement is blocked until the assignment is complete.

In a non-blocking procedural assignment, the expression is evaluated when the statement is encountered, and assignment is postponed until the end of the time-step. In a begin-end sequential statement group, execution of the next statement is not blocked and may be evaluated before the assignment is complete. A group of statements with a non-blocking assignment has similar functionality as a group of statements within a fork-join block.

The left-hand side of a procedural assignment should be one of the following:

- Register data type: reg , integer , time , real or realtime .

- Bit-select of reg , integer or time .

- Part-select of reg , integer or time .

- Memory word.

- Concatenation of any of the above.

When the right-hand side evaluates to a fewer bits than the left-hand side, the assignment to a reg does not sign-extend.

The evaluation of the assignment is delayed by the delay when the delay is specified before the register name. When the delay is specified before the expression, the expression is evaluated when the statement is encountered, and assigned in the time-step specified by the delay.

Continuous assignment , Expression , Net data type

- The Verilog-AMS Language

- Continuous Assigns

Continuous Assigns

A module may have any number of continuous assign statements. Continuous assign statements are used to drive values on to wires. For example:

This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire. The continuous assign statement is not a procedural statement and so must be used at the module level; it cannot be placed in an initial or always process.

You can add delay to a continuous assign statement as follows:

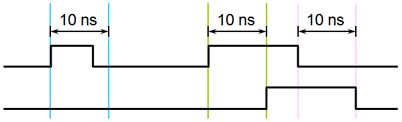

In this case, the value of a changes 10 units of time after the expression b & c changes. Continuous assign statement implement inertial delay, meaning that continuous assign statements swallow glitches. This is illustrated below with the assumption that the unit of time is 1ns.

It is possible to specify up to three delay values on a continuous assignment:

When you specify more than one:

The first delay refers to the transition to the 1 value (rise delay).

The second delay refers to the transition to the 0 value (fall delay).

The third delay refers to the transition to the high-impedance value.

When a value changes to the unknown (x) value, the delay is the smallest of the delays specified.

If only two delays are specified, then the delay to high-impedance is the smallest of the two values specified.

This guide aims to simplify the concepts of `wire` and `reg` in Verilog, explaining their roles and how they contribute to creating digital designs. Including the key distinctions and a table summary.

Wire vs Reg Data Types in Verilog: A Comprehensive Comparison

Introduction.

- Verilog HDL (Hardware Description Language) stands as a cornerstone in the realm of digital design and electronic systems development. Its ability to model and simulate the behavior of complex digital circuits has made it indispensable for engineers and designers worldwide.

- At the heart of Verilog’s functionality are its primary data types, reg and wire , which serve as the basic building blocks for describing hardware behavior and structure. There are other datatypes, but in this blog, the focus is on reg and wire as they are easily confused. Speaking from experience, distinguishing between these two was a challenge in my early days.

- These two data types help manage how information is handled in your designs. This guide aims to simplify these concepts, explaining their roles and how they contribute to creating digital designs. We’ll explain what reg and wire do and how they’re used differently, helping you make better choices in your designs.

The Role of Data Types in Verilog

- Understanding Verilog’s data types is essential as they directly represent the storage and transmission elements found in digital hardware.

- Verilog categorizes data types into nets and registers, each serving distinct roles in hardware modeling. Nets , for instance, are used for modeling physical connections between components and don’t store values, while registers are capable of storing values across procedural assignments, acting more like traditional variables in programming.

- This distinction is crucial for accurately designing and simulating digital circuits, highlighting Verilog’s versatility in modeling both the behavior and structure of electronic systems.

wire in Verilog

wire is a fundamental data type used to declare signals that connect different parts of a digital circuit, much like physical wires in hardware. These signals are very basic point-to-point connections within a design, primarily used to carry values between modules, gates, or other elements without storing any value themselves. This makes wire essential for modeling combinational logic , where the output is directly determined by the current inputs.

A typical use case for wire is in the implementation of simple logic gates within Verilog modules. For example, when defining an AND gate, you might declare a wire to hold the result of the AND operation between two inputs. This use of wire facilitates the simulation of the gate’s behavior in response to changes in input signals.

Limitations:

- However, wire types have their limitations. They cannot be used to store values over time or across different procedural blocks, such as within always blocks. This limitation makes wire unsuitable for situations where data needs to be retained or manipulated over time, a task better suited for the reg data type.

- All ports of this module are declared as wire because they are used for signal transmission within the circuit.

- Continuous Assignment : The assign statement continuously assigns the result of a & b to the result wire. This exemplifies how wire is used with continuous assignments to model the behavior of combinational logic.

reg in Verilog

reg is a versatile variable type primarily used to model digital circuits’ behavior. It’s designed to hold values across procedural assignments, meaning it can store a value until it’s changed by another assignment. This makes reg especially useful for representing data in sequential logic, like flip-flops, where the output depends on the sequence of input values over time. It’s also applicable in some cases for modeling combinational logic, where the output is a direct function of the input at any given moment.

reg is commonly utilized within always blocks, which are sections of Verilog code executed whenever specified signals change, effectively allowing the modeling of both combinational and sequential logic. For example, to model a flip-flop, a reg type variable would be assigned a new value based on the current inputs and the clock’s rising edge within an always block.

However, it’s important to note that while reg can be used to model hardware registers, its use does not directly imply the hardware will implement it as a physical register. The actual hardware implementation depends on the synthesis tool and the context of the reg ’s usage in the Verilog code.

- There are limitations and considerations when using reg . It’s not suitable for signals driven by multiple sources or for representing nets that connect different parts of a circuit.

- Because reg is designed to store values across procedural blocks, not to directly represent the behavior of combinational logic, otherwise, it would generate a unexpected latches.

- For example, when modeling a bus, which is a collection of signals that can be driven by different modules, wire would be the appropriate data type to use. Or when creating an AND gate, the output would be declared as wire since it’s a direct result of multiple inputs. For these cases, the wire type is used for signals that can be driven by multiple sources through continuous assignments.

- Inputs are declared as wire by default since they directly connect to external signals.

- The output q is declared as reg since it will hold a value across different clock cycles until explicitly changed.

- Always Block : The always block triggers on the rising edge of either the clk or the rst signal. This block contains procedural statements that describe how the output q should behave when these events occur.

Key Distinctions and Table Summary

- The choice between reg and wire hinges on the specific requirements of the digital design task at hand—whether it involves direct signal transmission or the need to maintain state over time. By understanding these distinctions and their appropriate applications, designers can effectively use Verilog to model and simulate a wide range of digital circuits, from simple logic gates to complex sequential systems, with accuracy and efficiency.

Procedural Assignments

Cite this chapter.

Part of the book series: The International Series in Engineering and Computer Science ((SECS,volume 667))

637 Accesses

This is a preview of subscription content, log in via an institution to check access.

Access this chapter

- Available as PDF

- Read on any device

- Instant download

- Own it forever

- Compact, lightweight edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

- Durable hardcover edition

Tax calculation will be finalised at checkout

Purchases are for personal use only

Institutional subscriptions

Unable to display preview. Download preview PDF.

Rights and permissions

Reprints and permissions

Copyright information

© 2002 Kluwer Academic Publishers

About this chapter

(2002). Procedural Assignments. In: Verilog® Quicstart. The International Series in Engineering and Computer Science, vol 667. Springer, Boston, MA. https://doi.org/10.1007/0-306-47680-0_7

Download citation

DOI : https://doi.org/10.1007/0-306-47680-0_7

Publisher Name : Springer, Boston, MA

Print ISBN : 978-0-7923-7672-9

Online ISBN : 978-0-306-47680-8

eBook Packages : Springer Book Archive

Share this chapter

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Publish with us

Policies and ethics

- Find a journal

- Track your research

Search code, repositories, users, issues, pull requests...

Provide feedback.

We read every piece of feedback, and take your input very seriously.

Saved searches

Use saved searches to filter your results more quickly.

To see all available qualifiers, see our documentation .

- Notifications

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement . We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

[FIRRTL] (mem) Procedural assignment to wire #1705

drom commented Sep 3, 2021

seldridge commented Sep 7, 2021

Sorry, something went wrong.

darthscsi commented Sep 8, 2021

lattner commented Sep 9, 2021

Darthscsi commented sep 9, 2021.

No branches or pull requests

Verilog Pro

Verilog reg, Verilog wire, SystemVerilog logic. What’s the difference?

The difference between Verilog reg and Verilog wire frequently confuses many programmers just starting with the language (certainly confused me!). As a beginner, I was told to follow these guidelines, which seemed to generally work:

- Use Verilog reg for left hand side (LHS) of signals assigned inside in always blocks

- Use Verilog wire for LHS of signals assigned outside always blocks

Then when I adopted SystemVerilog for writing RTL designs, I was told everything can now be “type logic”. That again generally worked, but every now and then I would run into a cryptic error message about variables, nets, and assignment.

So I decided to find out exactly how these data types worked to write this article. I dug into the language reference manual, searched for the now-defunct Verilog-2005 standard document, and got into a bit of history lesson. Read on for my discovery of the differences between Verilog reg , Verilog wire , and SystemVerilog logic .

Verilog data types, Verilog reg, Verilog wire

Verilog data types are divided into two main groups: nets and variables. The distinction comes from how they are intended to represent different hardware structures.

A net data type represents a physical connection between structural entities (think a plain wire), such as between gates or between modules. It does not store any value. Its value is derived from what is being driven from its driver(s). Verilog wire is probably the most common net data type, although there are many other net data types such as tri , wand , supply0 .

A variable data type generally represents a piece of storage. It holds a value assigned to it until the next assignment. Verilog reg is probably the most common variable data type. Verilog reg is generally used to model hardware registers (although it can also represent combinatorial logic, like inside an always@(*) block). Other variable data types include integer , time , real , realtime .

Almost all Verilog data types are 4-state, which means they can take on 4 values:

- 0 represents a logic zero, or a false condition

- 1 represents a logic one, or a true condition

- X represents an unknown logic value

- Z represents a high-impedance state

Verilog rule of thumb 1 : use Verilog reg when you want to represent a piece of storage, and use Verilog wire when you want to represent a physical connection.

Assigning values to Verilog reg, Verilog wire

Verilog net data types can only be assigned values by continuous assignments. This means using constructs like continuous assignment statement ( assign statement), or drive it from an output port. A continuous assignment drives a net similar to how a gate drives a net. The expression on the right hand side can be thought of as a combinatorial circuit that drives the net continuously.

Verilog variable data types can only be assigned values using procedural assignments. This means inside an always block, an initial block, a task , a function . The assignment occurs on some kind of trigger (like the posedge of a clock), after which the variable retains its value until the next assignment (at the next trigger). This makes variables ideal for modeling storage elements like flip-flops.

Verilog rule of thmb 2 : drive a Verilog wire with assign statement or port output, and drive a Verilog reg from an always block. If you want to drive a physical connection with combinatorial logic inside an always@(*) block, then you have to declare the physical connection as Verilog reg .

SystemVerilog logic, data types, and data objects

SystemVerilog introduces a new 2-state data type—where only logic 0 and logic 1 are allowed, not X or Z—for testbench modeling. To distinguish the old Verilog 4-state behaviour, a new SystemVerilog logic data type is added to describe a generic 4-state data type.

What used to be data types in Verilog, like wire , reg , wand , are now called data objects in SystemVerilog. Wire , reg , wand (and almost all previous Verilog data types) are 4-state data objects. Bit , byte , shortint , int , longint are the new SystemVerilog 2-state data objects.

There are still the two main groups of data objects: nets and variables. All the Verilog data types (now data objects) that we are familiar with, since they are 4-state, should now properly also contain the SystemVerilog logic keyword.

There is a new way to declare variables, beginning with the keyword var . If the data type (2-state or 4-state) is not specified, then it is implicitly declared as logic . Below are some variable declaration examples. Although some don’t seem to be fully supported by tools.

Don’t worry too much about the var keyword. It was added for language preciseness (it’s what happens as a language evolves and language gurus strive to maintain backward-compatibility), and you’ll likely not see it in an RTL design.

I’m confused… Just tell me how I should use SystemVerilog logic!

After all that technical specification gobbledygook, I have good news if you’re using SystemVerilog for RTL design. For everyday usage in RTL design, you can pretty much forget all of that!

The SystemVerilog logic keyword standalone will declare a variable, but the rules have been rewritten such that you can pretty much use a variable everywhere in RTL design. Hence, you see in my example code from other articles, I use SystemVerilog logic to declare variables and ports.

When you use SystemVerilog logic standalone this way, there is another advantage of improved checking for unintended multiple drivers. Multiple assignments, or mixing continuous and procedural ( always block) assignments, to a SystemVerilog variable is an error, which means you will most likely see a compile time error. Mixing and multiple assignments is allowed for a net. So if you really want a multiply-driven net you will need to declare it a wire .

In Verilog it was legal to have an assignment to a module output port (declared as Verilog wire or Verilog reg ) from outside the module, or to have an assignment inside the module to a net declared as an input port. Both of these are frequently unintended wiring mistakes, causing contention. With SystemVerilog, an output port declared as SystemVerilog logic variable prohibits multiple drivers, and an assignment to an input port declared as SystemVerilog logic variable is also illegal. So if you make this kind of wiring mistake, you will likely again get a compile time error.

SystemVerilog rule of thumb 1 : if using SystemVerilog for RTL design, use SystemVerilog logic to declare:

- All point-to-point nets. If you specifically need a multi-driver net, then use one of the traditional net types like wire

- All variables (logic driven by always blocks)

- All input ports

- All output ports

If you follow this rule, you can pretty much forget about the differences between Verilog reg and Verilog wire ! (well, most of the time)

When I first wondered why it was possible to always write RTL using SystemVerilog logic keyword, I never expected it to become a major undertaking that involved reading and interpreting two different specifications, understanding complex language rules, and figuring out their nuances. At least I can say that the recommendations are easy to remember.

I hope this article gives you a good summary of Verilog reg , Verilog wire , SystemVerilog logic , their history, and a useful set of recommendations for RTL coding. I do not claim to be a Verilog or SystemVerilog language expert, so please do correct me if you felt I misinterpreted anything in the specifications.

- Synthesizing SystemVerilog : Busting the Myth that SystemVerilog is only for Verification

- 1800-2012 – IEEE Standard for SystemVerilog–Unified Hardware Design, Specification, and Verification Language

- 1364-2005 – IEEE Standard for Verilog Hardware Description Language

- A lively discussion in Google Groups on SystemVerilog var keyword

Sample Source Code

The accompanying source code for this article is a SystemVerilog design and testbench toy example that demonstrates the difference between using Verilog reg, Verilog wire, and SystemVerilog logic to code design modules. Download the code to see how it works!

[lab_subscriber_download_form download_id=8].

Share this:

- Click to share on LinkedIn (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on Facebook (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

16 thoughts on “Verilog reg, Verilog wire, SystemVerilog logic. What’s the difference?”

Good article. However, there is one significant gotcha that users need to be aware of. When converting RTL from wire/reg to logic, if you were using a net declaration assignment for a wire, that will not work with logic! As a variable type, assigning a value to a logic variable as part of the declaration merely initializes it to that value. No continuous assignment is inferred.

This is the only case where logic has not been a drop-in replacement for me in RTL.

Example: wire mysignal0 = A & B; // continuous assignment, AND gate logic mysignal1 = A &B; // not synthesizable, initializes mysignal1 to the value of A & B at time 0 and then makes no further changes to it. logic mysignal2; assign mysignal2 = A & B; // Continuous assignment, AND gate

Thanks for pointing that out Evan! I looked through the assignment section of the LRM and you’re correct. Like you said, the particular form of assignment in the first row of your example code is called net declaration assignment (section 10.3.1 of SV-2012 LRM), and as the name suggests it only works on nets. The second line in your example is a variable declaration assignment (section 10.5), and would only initialize the variable and not continuously drive it. That is indeed a gotcha if one just replaced all instances of wire with logic. Great comment!

Would the rules of Verilog concerning blocking assignments(=) for combinational logic always blocks and non-blocking assignments(<=) for sequential logic always block also apply to SystemVerilog ?

Hi Varun. Yes, the same rules would apply when using SystemVerilog logic. You’ll have to be more careful about which SystemVerilog logic signal is intended to be combinational and which is intended to be sequential, because they will look the same in their declaration.

i have an old power verilog model it. i am re-using it and it is giving issues in compilation

it has a statement as below: bit power_on; assign power_on = vddmp & !gndmp;

now compilation is expecting some parentheses at end of “bit power_on;” statement

can anybody help how to solve this compilation issue thanks

Hi Shaily. Thanks for your comment. Are vddmp and gndmp functional signals? Or are they power supplies?

Thanks for a very nice article.

I have a very basic question about the logic design & Verilog.

As far as I know, it is not recommended to have combinational logic include

memory such as flip-flop and latch because it is combinational!

And that is the reason why inferred flip-flops & latch should be avoided,

which is induced by not including all inputs within sensitivity list in always block, uninitialized output, etc.

My question is if the reg variable inside the always *@ block holds the value until the next assignment, it may induce the flip-flops or latches.

Is it allowed to induce a latch or flip-flop inside the combinational logic with some intentions?

Thanks a lot

Hi Jaehyuk. A always@* block will be sensitive to all input signals to the block (with one exception). Therefore, if you use a reg type inside a always@* block, it will become combinational logic and not infer flip-flop or latches.

The one exception is if the always@* calls a function or task, and that function or task contains signals that are external to the function, task, and always@* block. SystemVerilog always_comb avoids this issue, so if you code in SystemVerilog, you should use always_comb instead of always@*. See my other article on always_comb and always_ff

Helpful article, thank you Jason.

Quote: wire [7:0] my_wire_bus; // implicitly means “wire logic[15:0] my_wire_bus”

Is there a minimal width of 16 bit in SystemVerilog or something?

No there isn’t. That just happens to be the example I came up with.

Nice write-up, thanks Jason! BTW, its a nice blog, please keep it up !

Thank you, Jason, for the article! One issue I see in replacing reg with logic is that it eliminates X from the variable. That way you may miss initialization problem. I think also using UPF will force X on the registers during power-down for verification. I am not sure that with that practice it will be compatible with UPF. What do you think?

Hi Dmitry. Using the logic keyword on its own actually declares a 4-state variable, so X’s can also be represented. There is no problem with representing X’s when using UPF, low power simulation, or x-propagation. I have used logic variables successfully on projects that use all these methodologies.

Good article. I certainly appreciate this site. Keep it up! buy viagra

Hi Jason, Your articles are really helpful. Can you post something related to UVM?

Leave a Comment Cancel reply

Notify me of follow-up comments by email.

Notify me of new posts by email.

This site uses Akismet to reduce spam. Learn how your comment data is processed .

Error (10137): Verilog HDL Procedural Assignment error at LED.v(27): object "LED_Out" on left-hand side of assignment must have a variable data type

Error (10137): verilog hdl procedural assignment error at main.v(209): object "juiceshuliang" on left-hand side of assignment must have a variable data type, error (10137): verilog hdl procedural assignment error at traffic_light.v(13.

DE1_SoC.zip_DE1_SoC_assignment_de1-soc_verilog

Verilog_led.rar_de2_de2-70_verilog l_verilog l

Key_led.zip_basys 2 流水灯 verilog_key_led.v_basys2开发板_basys2流水灯_fp.

procedural assignment to a non

Verilog三元运算符 ?:, verilog常考知识点, verilog assig, verilog中$是什么意思, in_out_put.rar_ram verilog_out_site:www.pudn.com, hc164.rar_164_led 164 vhdl_hc164_top_hc164_driver.v_verilog hc16, pwm_veriloghdl.rar_pwm verilog hdl _vhdl-fpga-verilog_altera_pw, key_led.zip_ise按钮控制灯_key_led_quartus控制led灯_veriloghdl key_verilo, led-light.rar_verilog led_verilog 点灯_fpga led verilog_fpga点灯程序_点, 安卓桌面应用eyeroom.zip, 仿随手记的炫酷饼图.zip, webview重载使用&自定义网址.zip, c语言学习工程和c语言项目.zip.

webview重载使用&自定义网址.zip

带暂停功能倒计时timecountdown盒子适用.zip.

2023年中国辣条食品行业创新及消费需求洞察报告.pptx

学习率衰减策略及调参技巧:在CNN中的精准应用指南

如何让restTemplate call到一个mock的数据

2023年半导体行业20强品牌.pptx.

IMAGES

VIDEO

COMMENTS

The procedural assign and deassign statements can be a source of design errors and can be an impediment to tool implementation. The procedural assign and deassign statements do not provide a capability that cannot be done by another method that avoids these problems. Therefore, the procedural assign and deassign statements are on a deprecation ...

wire penable = 1; Procedural Continuous Assignment. These are procedural statements that allow expressions to be continuously assigned to nets or variables and are of two types. assign... deassign; force... release; assign deassign. This will override all procedural assignments to a variable and is deactivated by using the same signal with ...

Continuous Assignment. Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types. module Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2;

Yes, they are equivalent. IEEE Std 1364-2005, section 6.2 Procedural assignments states:...procedural assignments put values in variables. The assignment does not have duration; instead, the variable holds the value of the assignment until the next procedural assignment to that variable. You do not need to use the 2nd code example.

Description: Procedural assignments are used for updating register data types and memory data types. The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered. In a begin-end sequential statement group, execution of the next statement is blocked until the assignment is complete. In a non ...

assign A = B; versus. alway_comb A = B; In this example, like many other constructs in Verilog, there is overlapping functionality. One of the biggest differences is that only the assign statement can be used to make an assignment to a net/wire. In SystemVerilog, you can use either statement to make assignments to a variable.

CSE 371 (Roth): Verilog Primer 7 Wire Assignment •Wire assignment: "continuous assignment" •Connect combinational logic block or other wire to wire input •When RHS changes, RHS re-evaluated and re-assigned •Designated by the keyword assign wire a, b, c; assign c = a | b; wire a, b, c = a | b; // same thing •Some new operations

Assign statements are used to implement set and reset because they dominate over the non-blocking assignment used to update q upon positive edges of the clock c.If instead a simple procedural assignment were used instead, then a positive edge on the clock could change q even if r or s were high.. A force statement is similar to assign, except that it can be applied to both registers and nets.

Procedural Assignments are a central aspect of SystemVerilog that are used to define the behavior of variables within procedural blocks such as initial, always, task, and function.These types of assignments differ significantly from Continuous Assignments as they are executed sequentially, following the flow of control in the procedural block, and not instantly upon changes to dependent variables.

Procedural assignments are used for updating register data types and memory data types. The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered.

Continuous assign statements are used to drive values on to wires. For example: assign a = b & c; This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire.

A wire represents a physical wire in a circuit and is used to connect gates or modules. The value of a wire can be read, but not assigned to, in a function or block. See " Functions" on p. 19, and "Procedures: Always and Initial Blocks" on p. 18. A wire does not store its value but must be driven by a continuous assignment statement or ...

This exemplifies how wire is used with continuous assignments to model the behavior of combinational logic. reg in Verilog. reg is a versatile variable type primarily used to model digital circuits' behavior. It's designed to hold values across procedural assignments, meaning it can store a value until it's changed by another assignment.

The destination of a procedural assignment is never a wire. The procedural assignment is one of three types of assignments you will learn in Verilog. For now, just remember that the left-hand side of a procedural assignment is a reg. The left-hand side can contain an integer, time, or real, but these data types can be thought of as abstractions ...

You signed in with another tab or window. Reload to refresh your session. You signed out in another tab or window. Reload to refresh your session. You switched accounts on another tab or window.

What used to be data types in Verilog, like wire, reg, wand, are now called data objects in SystemVerilog. Wire, reg, wand (and almost all previous Verilog data types) are 4-state data objects. Bit, byte, shortint, int, longint are the new SystemVerilog 2-state data objects. There are still the two main groups of data objects: nets and variables.

verilog编程中,"procedural assignment to a non"是一种常见的错误提示,意思是在一个非寄存器类型的变量上使用了过程赋值语句。 ... Verilog assign statement is used to assign a value to a wire or reg data type in a continuous assignment. It is commonly used to specify the interconnections between different ...

A wire in Verilog is very distinct concept from a variable.Although both are used to represent values that change over time, the way that obtain their values is very different. As in most other programming languages, you make a procedural assignment of a value to variable, and the variable holds that value until the next procedural assignment.. A wire represents a connection in hardware, or ...

6. Yes, you can use a wire's value inside an always block, you just can not assign a value to a wire in always or initial block. The only real difference between a wire and reg is the syntax for assigning values. In the above example d could also have been created as a wire, these are equivalent: reg [3:0] answer_reg; always @* begin.